霜月に入り秋になったら計画(仮称)という事で:)11月にその11としてHC11関連のトピックを書いてみます。とはいえ過去ではなく現在の事柄(所謂、レトロマイコン製作関連)ではありますが。

0.MC68HC11Fにつきまして

https://www.nxp.com/docs/en/data-sheet/MC68HC11FTS.pdf

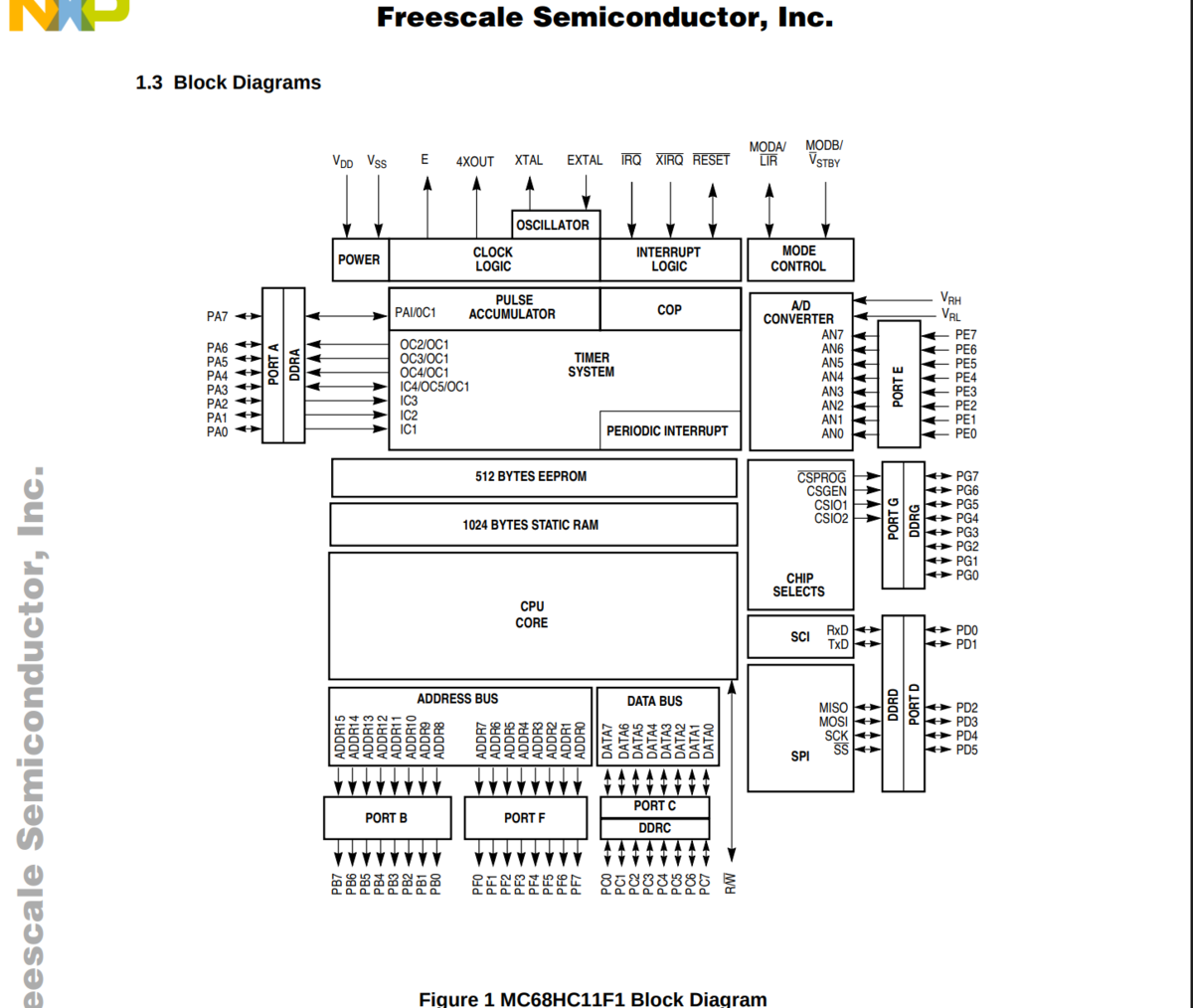

2025年の現在でも本家サイトでデータシートが閲覧出来るのはモトローラ時代からの善き伝統(こういうのをDNAと呼ぶべきと思いますよ)でブロック図を以下に引用します↓

特徴はHC11ファミリにしては珍しく(A/Eのイメージが強いので)ノンマルチプレクスバスになってます、つまり普通のマイコンと同じでアドレス、データは独立して出力されている。その為かどうかは知れぬがHC11にしては高め(5〜6Mhz)のバージョンも存在する様です。

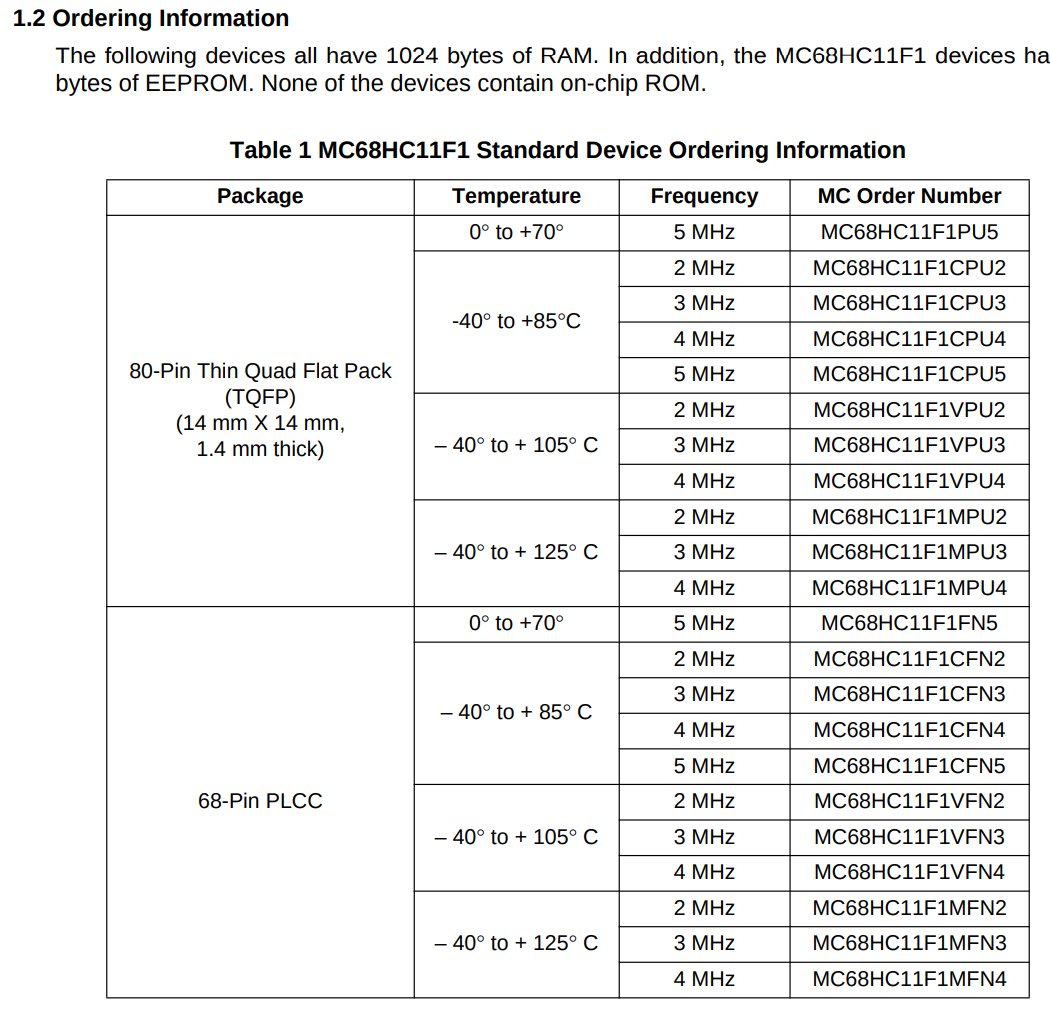

当方が入手したMC68HC11F1FN(元祖秋葉原さんから入手したもの)はこのテーブルによると0〜70℃で5Mhz動作(外部クロック/Xtalは20Mhz)に相当する様なしない様な・・・チップのFNの後は空白で少なくとも5は印刷されていない様な・・・まあ、テストするのは自由ですから5Mhz/6Mhz/8Mhz(外部クロック32Mhz)で動かしてみた(所謂オーバクロックですね。良い子は真似してはいけません:)で常温(雰囲気26℃程度)で数十分程度では何とも無かった(TPがLチカなので・・・)みたいな・・・

通常のMC68HC11(A/E)は2Mhzで3Mhz品も存在する程度の認識でいたのですがF1になると5Mhz(ADC:PORTE等を使わないFC0であれば6Mhz動作もすると書いてある)と2.5倍動作する・・・かもしれないと(まあ、Ghzオーダのご時世に今更5Mhzと言われてもなのですが)。

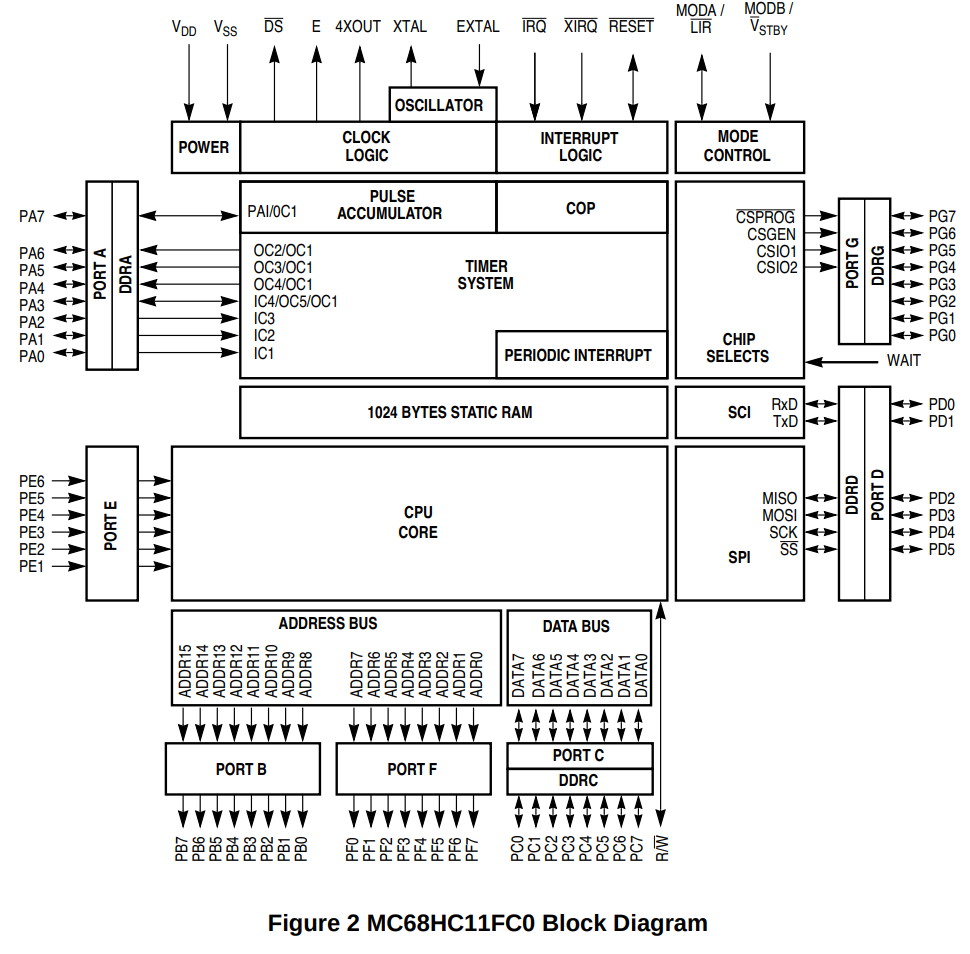

これによるとMC68HC11FC0はbus speedが6Mhz行けると記載さえている様です(eepromもadcも無いけど)邪推するに当時の競争(H8とか?)が激しかったのか結構無理してる様な印象も少々。。。

とまあ与太話はこの辺にして、

1.hc11f_v1(仮称)

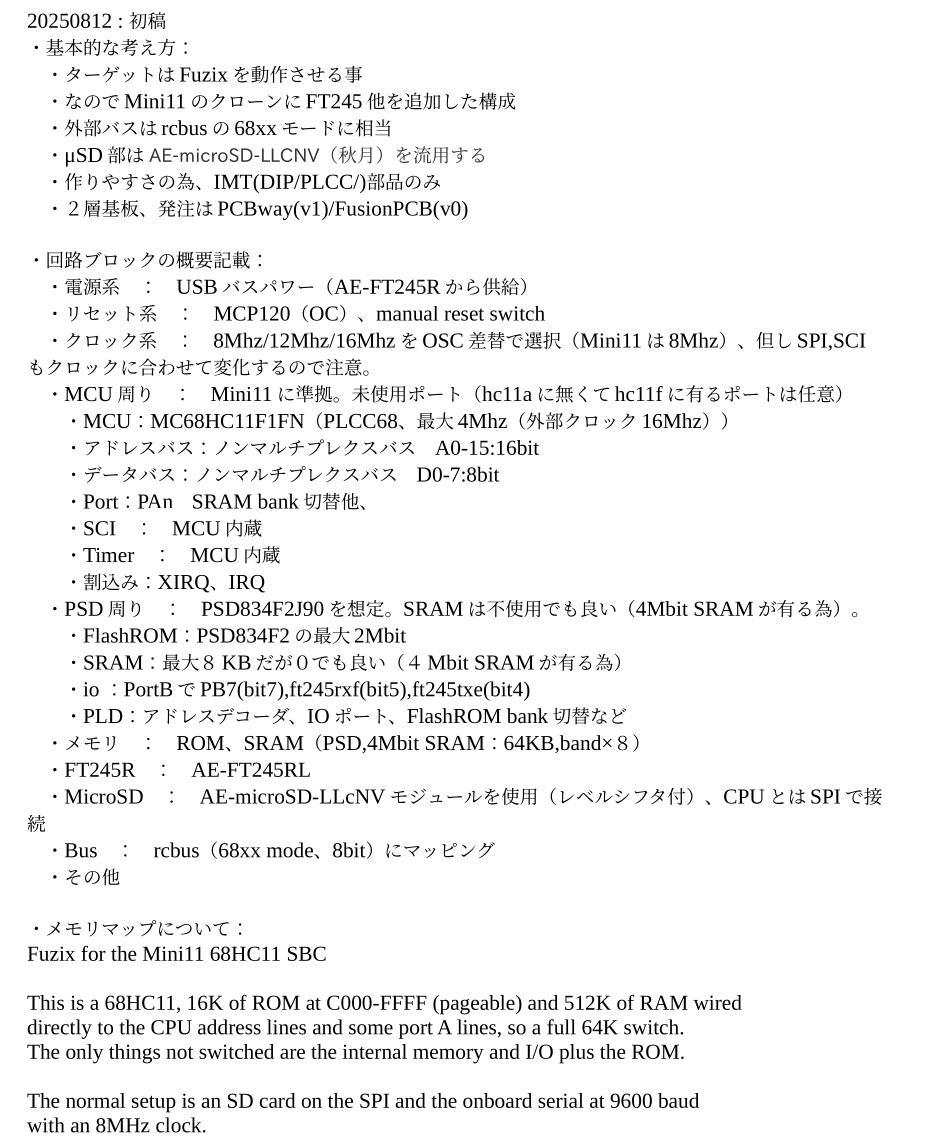

資料を書こうの再掲になるのですがお粗末ですが作成した資料を参照しつつ、

・基本的な考え方

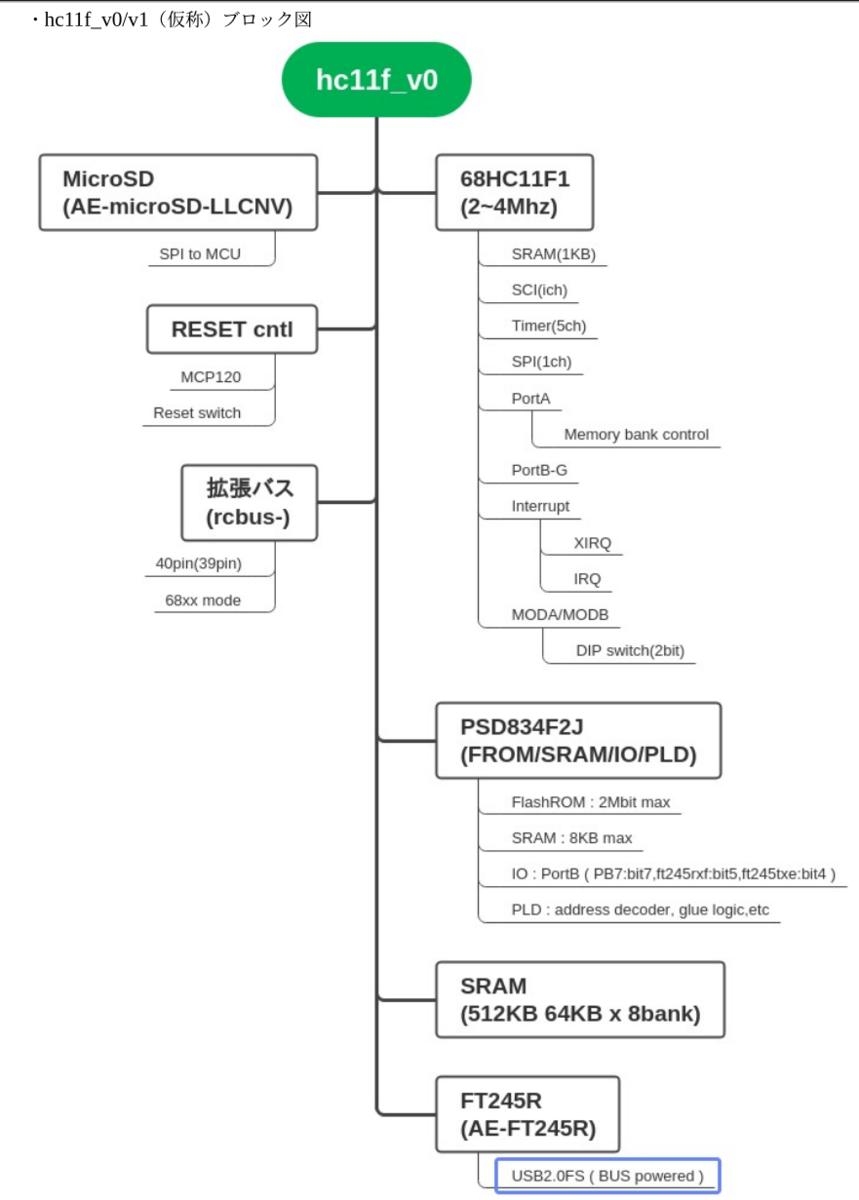

・ブロック図

・概略仕様とメモリマップ

実はこれには元ネタがありましてFuzix本家サイトで紹介されたMini11が相当します↓

このプロジェクトはMC68HC11A1(DIP)で構成されたコンパクトな物ですが、(止せば良いのに)元祖秋葉原さんで入手可能なMC68HC11F1を素材にしてアレンジしてみようと製作したのが今回のボードであります(上記ブロック図ですね)。

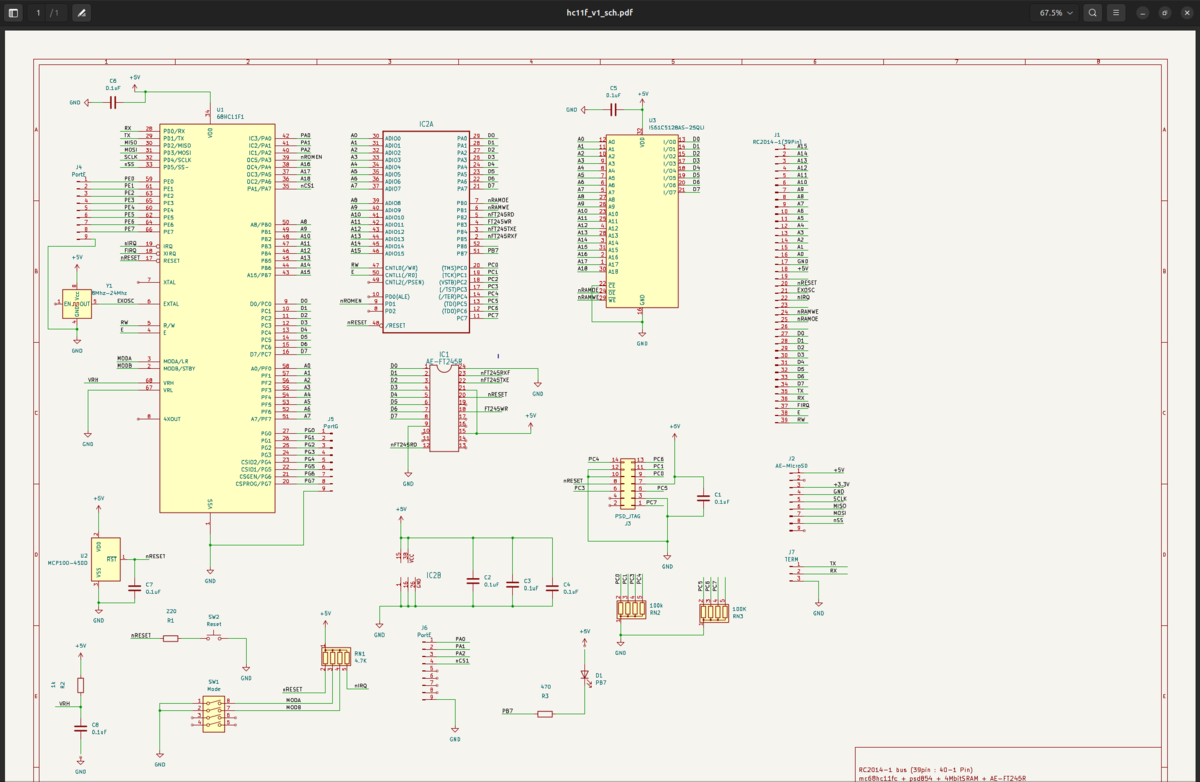

・回路図

・パターン図(全レイヤ合成)

・詳細につきましては上記資料をご参照下さい(作成中につき不正確な箇所がある可能性があります、すみません。)

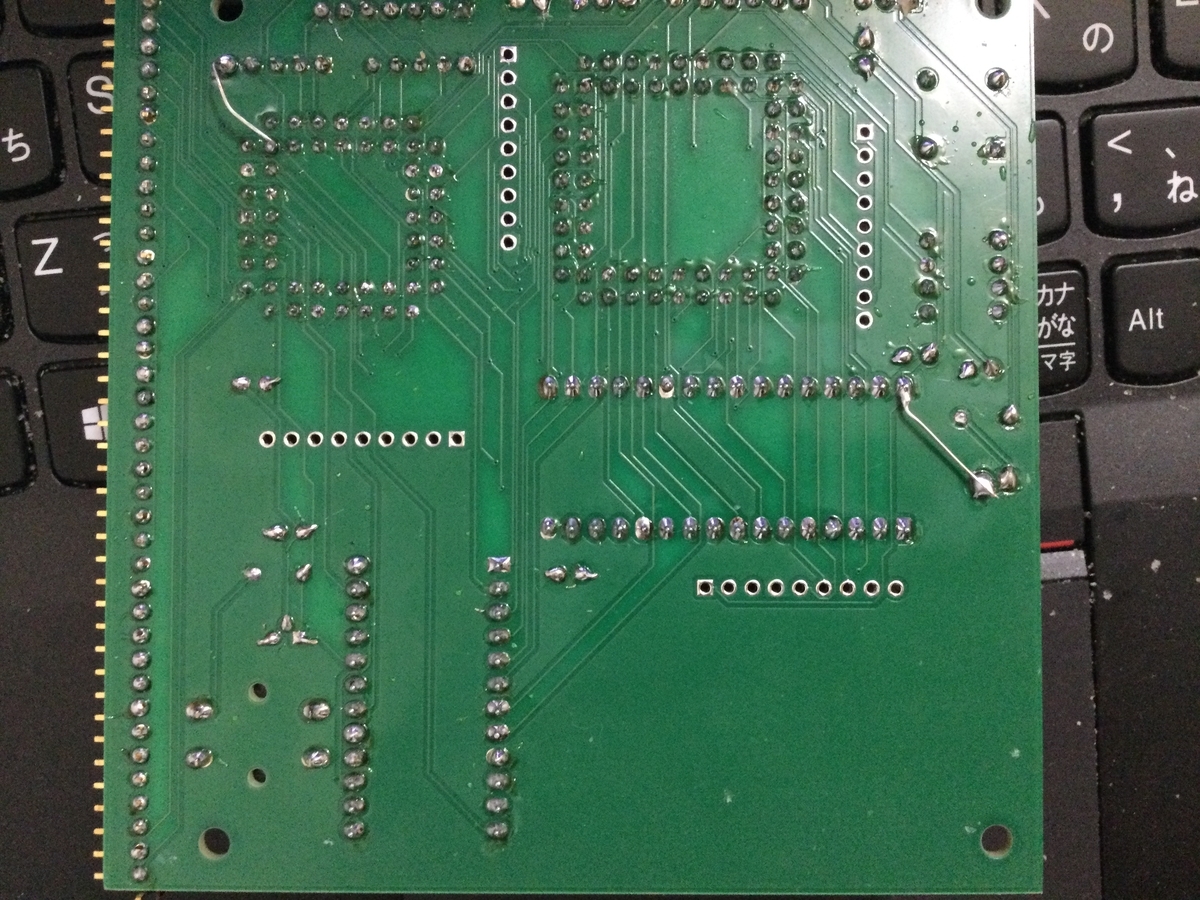

2.実装ボード(実物)

ご覧のとおりの100✕100mm、2層の基板でこれは無論中華基板メーカさん(当方はPcbWayを利用)でのキャンペーン価格適用の為です(他社も追従されている様で、所謂レッドオーシャン的な・・・)。

左上がMCU(MC68HC11F1FN)でPLCC68なので68000と同じ大きさであります(8ビットなんですがね)その右に居るのが(私が大好きな)PSD834F2J90チップでこれ1個でFlash/PLD/GPIO/SRAMをISP出来るという代物です。

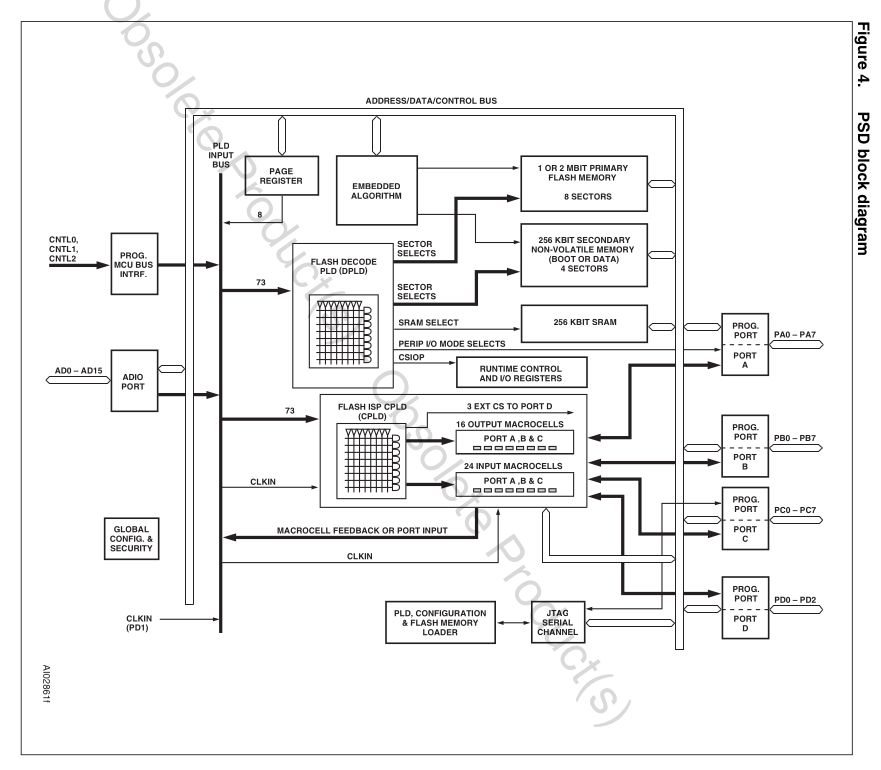

しつこいかもしれませんが、PSD8XXのブロック図を以下に示しておきます。昨今ではMCUに統合されておりますが、1990〜2000年初期ではこの様なMCUとペアで使うFlash/SRAM/PLD/IOというチップが存在しておりました。

元々イスラエルのWSI社(バイポーラ置換の高速ROM/SRAM等も手掛けていた会社です)が開発した製品ですが、ST社に買収されSTの製品系列に組込まれ、STではμPSDという名称で8032コア+PSDでシングルチップsolution等も提供されておりました。

なので開発ツールベンダのResonance社:STと馴染みが深いST7等の開発ツールを提供していたベンダ、rlinkも中はST72で構成されている(この辺は当方の独自解釈の可能性があります):が提供するrlinkにパラレルポート時代のFlashLink(WSI時代からのパラレルポートのプログラマ、当時はXもAもパラレルポートの書込器が当たり前でした)の機能をrlinkのHWを使って(結局の処、JTAGプログラマ/デバッガなので)PSDSoftExpressにUSB対応のプログラマを組み込んだのではと想像しております。

#まあ、そのおかげで2025年の現在でもdigi-key等で開発ツール(だけ)は入手出来る訳ですが(残念ながらXやAの様な互換中華ツールは存在しない様です)↓

実は某オークションサイトで入手可能である事を知り、大人買いしてしまいました:)多少値は張りましたがISP無しでは生きていけない体になってしまったので(あはは)・・・

20251105追記:PLDの論理式を以下に示します。PSDAbelなるAbel(エーベルと当時は読んでおりました。DataIO社の開発したPLD用論理合成言語です。今どきのHDLを嗜む方にとっては原始的かもしれませんが理解しやすいと思います:)

******************************************************************************************

PSDsoft Express Version 8.66

Output of PSD Fitter

******************************************************************************************

PROJECT : hc11f_v0 DATE : 11/05/2025

DEVICE : PSD834F2 TIME : 16:03:03

FIT OPTION : Keep Current

DESCRIPTION: 20250816:mc68hc11f1 for fuzix design ( hc11f_v0 )・・0251025

buffalo uses different memory map (rom:0xe000-0xffff,ram:0x0-0xbfff)・

******************************************************************************************

==== Pin Layout for J (52-Pin PLCC) Package Type ====-----------------------------

| |

|1 ] GND pa2 [27| Data Port d2, d2

nFT245RXF |2 ] pb5 pa1 [28| Data Port d1, d1

nFT245TXE |3 ] pb4 pa0 [29| Data Port d0, d0

FT245WR |4 ] pb3 adio0 [30| Address Bus a0, a0

nFT245RD |5 ] pb2 adio1 [31| Address Bus a1, a1

nRAMWE |6 ] pb1 adio2 [32| Address Bus a2, a2

nRAMOE |7 ] pb0 adio3 [33| Address Bus a3, a3

|8 ] pd2 adio4 [34| Address Bus a4, a4

|9 ] pd1 adio5 [35| Address Bus a5, a5

|10] pd0 adio6 [36| Address Bus a6, a6

|11] pc7 adio7 [37| Address Bus a7, a7

tdo, TDO |12] pc6/TDO VCC [38|

tdi, TDI |13] pc5/TDI adio8 [39| Address Bus a8, a8

|14] pc4/TERR adio9 [40| Address Bus a9, a9

|15] VCC adio10 [41| Address Bus a10, a10

|16] GND adio11 [42| Address Bus a11, a11

|17] pc3/TSTAT adio12 [43| Address Bus a12, a12

|18] pc2 adio13 [44| Address Bus a13, a13

tck, TCK |19] pc1/TCK adio14 [45| Address Bus a14, a14

tms, TMS |20] pc0/TMS adio15 [46| Address Bus a15, a15

d7 ,Data Port d7 |21] pa7 cntl0 [47| r_w

d6 ,Data Port d6 |22] pa6 reset [48| _reset

d5 ,Data Port d5 |23] pa5 cntl2 [49| nROMEN

d4 ,Data Port d4 |24] pa4 cntl1 [50| e

d3 ,Data Port d3 |25] pa3 pb7 [51| pb7

|26] GND pb6 [52|

| |

-----------------------------

==== Global Configuration ====Data Bus : 8-Bit

Address/Data Mode : Non-Multiplexed

ALE/AS Signal : Off

Control Signals : R/W, E

Enable Chip-Select Input(/CSI) : OFF

Standby Voltage Input (PC2) : OFF

Standby-on Indicator (PC4) : OFF

RDY/Busy function (PC3) : OFF

Load Micro-Cell on : edge

Security Protection : OFF==== Address & Data Bus Assignment ====

Stimulus Bus Name Signal Description

---------------------------------------------------------

`adiol = adio[7:0] = Address Bus a[7:0]

`adioh = adio[15:8] = Address Bus a[15:8]

adio = adio[15:0] = Address Bus a[15:0]data = data[7:0] = Data Port d[7:0]

==== DataBus_IMC access information ====CSIOP

Location Address Offset Register Name Signals

--------------------------------------------------------===== Resource Usage Summary =====

Total Product Terms Used: 23

Device Resources used / total

------------------------------------------------

Port A: (pins 29 28 27 25 24 23 22 21)

I/O Pins : 8 / 8

MCU I/O or Address Out : 0

Peripheral I/O : 0

Logic Inputs : 0

Address Latch Inputs : 0

PT Dependent Latch Inputs : 0

PT Dependent Register Inputs : 0

Combinatorial Outputs : 0

Registered Outputs : 0

Data Port : 8

Other Information

Microcells : 1 / 8

Micro-Cells AB :

Buried Microcells : 1

Output Microcells : 0

Product Terms : 3 / 24

Control Product Terms : 0 / 34Port B: (pins 7 6 5 4 3 2 52 51)

I/O Pins : 7 / 8

MCU I/O or Address Out : 3

Logic Inputs : 0

Address Latch Inputs : 0

PT Dependent Latch Inputs : 0

PT Dependent Register Inputs : 0

Combinatorial Outputs : 4

Registered Outputs : 0

Other Information

Microcells : 4 / 8

Micro-Cells AB :

Buried Microcells : 0

Output Microcells : 0

Micro-Cells BC :

Buried Microcells : 0

Output Microcells : 4

Product Terms : 8 / 28

Control Product Terms : 5 / 34Port C: (pins 20 19 18 17 14 13 12 11)

I/O Pins : 4 / 8

MCU I/O or Address Out : 0

Logic Inputs : 0

Address Latch Inputs : 0

PT Dependent Latch Inputs : 0

PT Dependent Register Inputs : 0

JTAG signals : 4

Standby Voltage Input : 0

Rdy/Bsy signal : 0

Standby On Indicator : 0

Control Signal Input : 0

Combinatorial Outputs : 0

Registered Outputs : 0

Other Information

Microcells : 4 / 8

Micro-Cells BC :

Buried Microcells : 4

Output Microcells : 0

Product Terms : 12 / 32

Allocated locally : 8

Allocated to other port : 4

Control Product Terms : 0 / 34Port D: (pins 10 9 8)

I/O Pins : 0 / 3

MCU I/O or Address Out : 0

Logic Inputs : 0

Chip-Select Input : 0

Clock Input : 0

Control Signal Input : 0

Fast Decoding Outputs : 0

Other Information

Product Terms : 0 / 3

Control Product Terms : 0 / 3

==== OMC Resource Assignment ====Resources PT User

Used Allocation Name

---------------------------------------------------------

Micro-Cell AB :

Micro-Cells 0 Yes fs0_0 => CombinatorialMicro-Cell BC :

Micro-Cells 0 - nRAMOE (mcellbc0) => Combinatorial

Micro-Cells 1 - nRAMWE (mcellbc1) => Combinatorial

Micro-Cells 2 - nFT245RD (mcellbc2) => Combinatorial

Micro-Cells 3 - FT245WR (mcellbc3) => CombinatorialExternal Chip Select :

========= Equations =========DPLD EQUATIONS :

=======================

fs0 = fs0_0.FB;csiop = !pdn & a15 & a14 & a13 & a12 & a11 & a10 & a9 & a8 & !a7 & !a6 & !a5 & !a4 & !a3;

PORTA EQUATIONS :

=======================

!fs0_0 = (!a15)

# (!a14)

# (a13 & a12 & a11 & a10 & a9 & a8 & !a7 & a6 & a5 & a4 & !a3)

# (a13 & a12 & a11 & a10 & a9 & a8 & !a7 & a6 & a5 & a4 & !a2)

# (!e)

# (!r_w)

# (nROMEN)

# (pdn);PORTB EQUATIONS :

=======================

nRAMOE = (!e)

# (!r_w)

# (!nROMEN & a15 & a14);

nRAMOE.OE = _reset;nRAMWE = (!e)

# (r_w)

# (!nROMEN & a15 & a14);

nRAMWE.OE = _reset;!nFT245RD = e & r_w & a15 & a14 & a13 & a12 & a11 & a10 & a9 & a8 & !a7 & a6 & a5 & a4 & a3 & !a2 & !a1 & !a0;

nFT245RD.OE = _reset;FT245WR = e & !r_w & a15 & a14 & a13 & a12 & a11 & a10 & a9 & a8 & !a7 & a6 & a5 & a4 & a3 & !a2 & !a1 & !a0;

FT245WR.OE = _reset;pb7.OE = _reset;

PORTC EQUATIONS :

=======================

PORTD EQUATIONS :

=======================

--- End ---

話を戻すと右下は秋月のAE-FT245RL(最近EOL対応で倍に値上がりした奴です)モジュールでUSB-パラレル変換の定番モジュールを使用しています。左中は4Mbit SRAMでdigi-keyでは1Mbit品と大差無いので4M品に揃えるのも手かもしれません。

そして左下の空間はこれまた秋月のmicroSD変換モジュールを搭載予定です。入手はしてあるのですが、コネクタ挿抜したくて(切り分けの為に直付したくなくて)ピンソケット入手待ち状態。

20251107 18:04追記:ピンソケット入手し、microSD変換モジュール実装しました。

最後に右サイドはrcbus/rc2014bus のコネクタ(ピンヘッダ)です。なので一応、rcbus/rc2014対応:)

ご覧の通りリードジャンパで改造箇所が2箇所。1つはD1(LED)のカソードがVCCと未結線(当方の回路図入力ミス、ERCのチェック基準を甘くし過ぎた(反省))、もう一つはPA3(nROMEN)のプルダウン処理漏れ(PA3とRN3のP05を接続)であります(現時点での虫取り状況において)。これでも目の調子が良い頃を見計らって作業したのですが・・・下手くそなハンダ付けですね(恥ずかし)。

3.開発環境

と申す程でもないのですが、虫取り中の写真をば↓

写真左が今回のボード:hc11f_v1(仮称)で下のAE-FT245RLのmini-Bにつながってるのがホスト(Thinkpad x1 tablet:二代目:)との電源・通信ケーブルであり、上のフラットケーブルがPSD834F2J90のISP用コネクタで写真右上の小さな基板(今回の為に変換基板起こしました。5USDで10枚なので楽勝)でrlinkの24Pin(元々ARM用です)コネクタでrlinkと接続し、ホスト上ではUbuntu24.04.3LTSホストのVMWareでゲストOSとしてWindowsXPhomeでPSDSoftExpressを動かしております。

#今までのワイヤー群のもじゃもじゃが解消されたので幾分スッキリした気分(物理的、心理的)。

今回は幸いロジアナ等の重装備を投入しなくて動作してくれたので(LA2016を確保してあるのですが)rlinkだけで済んだのは僥倖でありました。組立は10月31日の午後から始めて、LチカのTP書いて動作する様になったのが同日深夜でありました。その後11月1日に虫取り/改造を済ませて、11月2日(本ブログを書いている日)に後述するホストとの通信プログラム(dba:debug agentと命名:)を68000のアセンブラから68hc11のアセンブラにバックポートしてメモリR/W/goが出来る様になったのが今日の夕方ぐらいと珍しく当方にとっては短期間で済んだような(年齢補正すると)。。。

4.dba : debug agent(仮称)

LチカのTP書いた後に何らかのデバッグというかツールをROMに置かないと進まない訳ですが(buffalo32もアセンブルしていた)、FT245つまりUSBパラレルでホストと接続するとターゲット(今回はMC68HC11F1)のコードも少なくて済むのでm68030_v0(仮称)で苦し紛れに実装した物をhc11f_v1(仮称)にも組み込む事にしました。

AS V1.42 Beta [Bld 270] - Source File hc11f_t3.asm - Page 1 - 2025年11月02日 15時36分36秒

1/ 0 : cpu 6811

2/ 0 :

3/ 0 : ; 20251102 : hc11f_t3.asm 小さなrom debug agent風のもの

4/ 0 : ; : hc11f_t0.asmの環境引き継ぎ、

5/ 0 : ; : csiop = $ff00 - ff07

6/ 0 : ; : ft245 = $ff78

7/ 0 : ; : fs0 = $c000 - feff, ff80 - ffff

8/ 0 : ; : $f800-feff, $ff80-ffff がrom領域、$ff00-ff7fはcsiop+ft245のi/o領域

9/ 0 : ; : rs0 = 0(なし)

10/ 0 : ; : ram = $0000 - $bfff + pa3-6の構成による

11/ 0 : ; : work ram 領域:$bf00- , stack 〜$bfff に設定

12/ 0 : ; : hc11f ram = $f060 - f3ff, hc11f reg = $f000 - f05f

13/ 0 :

14/ 0 :

15/ 0 : =$F800 romtop equ $f800 ; $c000-ffffの中のどこか

16/ 0 : =$FF00 csiop equ $ff00 ; $ff00-ff07(256バイト境界)

17/ 0 : =$BF00 ramtop equ $bf00 ; $0000-bfff

18/ 0 : =$BFFF rambtm equ ramtop+$ff

19/ 0 : =$FF05 pb7 equ csiop+5 ; psd portb7

20/ 0 : =$FF01 pbin equ csiop+1 ; ft245 status

21/ 0 : =$FF78 ft245 equ $ff78 ; $ff78

22/ 0 : =$F000 porta equ $f000 ; 初期値

23/ 0 : =$F001 ddra equ porta+1 ; ddra

24/ 0 : =$103D initreg equ $103d ; init reg.

25/ 0 :

26/BF00 : org ramtop

27/BF00 :

28/BF00 : a0 rmb 2 ; pseduo a0

29/BF02 : a1 rmb 2

30/BF04 : a2 rmb 2

31/BF06 : a3 rmb 2

32/BF08 : a4 rmb 2

33/BF0A : a5 rmb 2

34/BF0C : a6 rmb 2

35/BF0E : d0 rmb 2 ; pseduo d0

36/BF10 : d1 rmb 2

37/BF12 : d2 rmb 2

38/BF14 : d3 rmb 2

39/BF16 : d4 rmb 2

40/BF18 : d5 rmb 2

41/BF1A : d6 rmb 2

42/BF1C : d7 rmb 2

43/BF1E :

44/F800 : org romtop

45/F800 :

46/F800 : =$5 dly_cnt equ 5

47/F800 :

48/F800 : 8E BF FF start lds #rambtm ; sp init

49/F803 :

50/F803 : 86 FF ldaa #$FF ; initregでram=reg=$f000に設定

51/F805 : B7 10 3D staa initreg ; 以後はhc11fのregは$f000-f05f,ramは$f060-f3ffにマッピング

52/F808 : 86 00 ldaa #0

53/F80A : B7 F0 00 staa porta ; pa3-6 を0に初期化 nROMEN,a16-a18(4Mbit sram)

54/F80D : 86 FF ldaa #$ff ; ddra 全て出力

55/F80F : B7 F0 01 staa ddra

56/F812 :

57/F812 : BD F8 B4 jsr pb7on ; pb7=on

58/F815 : BD F8 BC jsr dly

59/F818 : BD F8 AF jsr pb7off

60/F81B :

AS V1.42 Beta [Bld 270] - Source File hc11f_t3.asm - Page 2 - 2025年11月02日 15時36分36秒

61/F81B : ; cmd待ち

62/F81B : BD F8 AF cmd jsr pb7off

63/F81E : BD F8 8B jsr pbin0 ; cmd受信

64/F821 : BD F8 B4 jsr pb7on

65/F824 : C1 D1 cmpb #$d1 ; memory dump?

66/F826 : 26 04 bne cmd1

67/F828 : 8D 33 bsr memc ; cmd exec

68/F82A : 20 EF bra cmd

69/F82C : C1 D2 cmd1 cmpb #$d2 ; go?

70/F82E : 26 04 bne cmd2

71/F830 : 8D 33 bsr go ; go cmd

72/F832 : 20 E7 bra cmd

73/F834 : C1 D3 cmd2 cmpb #$d3 ; memory write?

74/F836 : 26 04 bne cmd0

75/F838 : 8D 08 bsr memw ; memw exec

76/F83A : 20 DF bra cmd

77/F83C : C1 D0 cmd0 cmpb #$d0 ; machine id?

78/F83E : 26 DB bne cmd

79/F840 : ;;; bsr id

80/F840 : 20 D9 bra cmd

81/F842 : ; memory write

82/F842 : 8D 35 memw bsr adrin ; 戻り値はDとする

83/F844 : FD BF 04 std a2 ; adrs = a2

84/F847 : 8D 30 bsr adrin

85/F849 : FD BF 18 std d5 ; length = d5

86/F84C : FE BF 04 ldx a2

87/F84F : 18 FE BF 18 ldy d5

88/F853 : 8D 36 memw0 bsr pbin0 ; accb

89/F855 : E7 00 stab 0,x ; (x)<=accb

90/F857 : 08 inx

91/F858 : 18 09 dey

92/F85A : 26 F7 bne memw0

93/F85C : 39 rts

94/F85D : ; memory dump

95/F85D : 8D 1A memc bsr adrin ; adrs = a2

96/F85F : FD BF 04 std a2

97/F862 : 8D 32 bsr dump

98/F864 : 39 rts

99/F865 : ; go

100/F865 : 8D 12 go bsr adrin ; adrs = a2

101/F867 : FE BF 04 ldx a2

102/F86A : AD 00 jsr 0,x ; subroutineとして呼び出し

103/F86C : B6 FF 01 go0 ldaa pbin ; ft245 rxf?

104/F86F : 85 10 bita #$10

105/F871 : 26 F9 bne go0

106/F873 : 86 00 ldaa #0

107/F875 : B7 FF 78 staa ft245 ; 常に00を返す

108/F878 : 39 rts

109/F879 :

110/F879 : adrin:

111/F879 : 8D 10 bsr pbin0 ; 上位2バイトは読み飛ばす

112/F87B : 8D 0E bsr pbin0

113/F87D : 8D 0C bsr pbin0 ; 戻り値はaccbに

114/F87F : F7 BF 02 stab a1

115/F882 : 8D 07 bsr pbin0

116/F884 : F7 BF 03 stab a1+1

117/F887 : FC BF 02 ldd a1 ; 戻り値 = D

118/F88A : 39 rts

119/F88B :

120/F88B : B6 FF 01 pbin0 ldaa pbin

AS V1.42 Beta [Bld 270] - Source File hc11f_t3.asm - Page 3 - 2025年11月02日 15時36分36秒

121/F88E : 84 20 anda #$20

122/F890 : 26 F9 bne pbin0

123/F892 : F6 FF 78 ldab ft245 ; 受信データ <- accb

124/F895 : 39 rts

125/F896 :

126/F896 : 18 CE 01 00 dump ldy #256

127/F89A : FE BF 04 ldx a2

128/F89D : B6 FF 01 dump0 ldaa pbin

129/F8A0 : 84 10 anda #$10

130/F8A2 : 26 F9 bne dump0

131/F8A4 : A6 00 ldaa 0,x

132/F8A6 : B7 FF 78 staa ft245 ; 送信データ

133/F8A9 : 08 inx

134/F8AA : 18 09 dey

135/F8AC : 26 EF bne dump0

136/F8AE : 39 rts

137/F8AF :

138/F8AF : 36 pb7off psha

139/F8B0 : 86 80 ldaa #$80 ; pb7 led off

140/F8B2 : 20 03 bra pb7set

141/F8B4 : 36 pb7on psha

142/F8B5 : 86 00 ldaa #0 ; pb7 led on

143/F8B7 : B7 FF 05 pb7set staa pb7

144/F8BA : 32 pula

145/F8BB : 39 rts

146/F8BC :

147/F8BC : 36 dly psha

148/F8BD : 86 05 ldaa #dly_cnt

149/F8BF : CE 00 00 dly0 ldx #0

150/F8C2 : 09 dly1 dex

151/F8C3 : 26 FD bne dly1

152/F8C5 : 4A deca

153/F8C6 : 26 F7 bne dly0

154/F8C8 : 32 pula

155/F8C9 : 39 rts

156/F8CA :

157/FFFE : org $fffe

158/FFFE : F8 00 resvec fdb start ; reset vector

159/10000 :

160/10000 : end

AS V1.42 Beta [Bld 270] - Source File hc11f_t3.asm - Page 4 - 2025年11月02日 15時36分36秒

Symbol Table (* = unused):

--------------------------*A0 : BF00 C | A1 : BF02 C |

A2 : BF04 C | *A3 : BF06 C |

*A4 : BF08 C | *A5 : BF0A C |

*A6 : BF0C C | ADRIN : F879 C |

*ARCHITECTURE : "x86_64-unknown-linux" - |

*CASESENSITIVE : 0 - | CMD : F81B C |

CMD0 : F83C C | CMD1 : F82C C |

CMD2 : F834 C | *CONSTPI : 3.141592653589793 - |

CSIOP : FF00 - | *D0 : BF0E C |

*D1 : BF10 C | *D2 : BF12 C |

*D3 : BF14 C | *D4 : BF16 C |

D5 : BF18 C | *D6 : BF1A C |

*D7 : BF1C C |

*DATE : "2025\-027\-071\-07611\-026\-100\-12002\-026\-105\-091" - |

DDRA : F001 - | DLY : F8BC C |

DLY0 : F8BF C | DLY1 : F8C2 C |

DLY_CNT : 5 - | DUMP : F896 C |

DUMP0 : F89D C | *FALSE : 0 - |

FT245 : FF78 - | GO : F865 C |

GO0 : F86C C | *HAS64 : 1 - |

INITREG : 103D - | *LISTON : 1 - |

*MACEXP : 7 - | MEMC : F85D C |

MEMW : F842 C | MEMW0 : F853 C |

*MOMCPU : 6811 - | *MOMCPUNAME : "6811" - |

*NESTMAX : 100 - | *PADDING : 0 - |

PB7 : FF05 - | PB7OFF : F8AF C |

PB7ON : F8B4 C | PB7SET : F8B7 C |

PBIN : FF01 - | PBIN0 : F88B C |

PORTA : F000 - | RAMBTM : BFFF - |

RAMTOP : BF00 - | *RELAXED : 0 - |

*RESVEC : FFFE C | ROMTOP : F800 - |

START : F800 C |

*TIME : "15\-026\-103\-12636\-027\-120\-12236\-025\-089\-110" - |

*TRUE : 1 - | *VERSION : 142F - |63 symbols

29 unused symbolsAS V1.42 Beta [Bld 270] - Source File hc11f_t3.asm - Page 5 - 2025年11月02日 15時36分36秒

Code Pages:

----------STANDARD (0 changed characters)

1 code page

0.07 seconds assembly time

162 lines source file

2 passes

0 errors

0 warnings

$F800-F8CA + リセットベクタ2バイトで220バイト程とコード変換やUI(CUIであっても)が無いとコンパクトになるものだと・・・もっとも80年代にはVTLで256バイトというツワモノが居たので軟弱ジジイの呟きに過ぎませんが。

でどこかで見た様な画面ですがpythonホスト側はそのまんま(タイトル変えただけ:)でdba(hc11f_v1側のromプログラム、上記リストでhc11f_t3.lstが相当)側で互換を取っております。具体的にはアドレス、レングスが32ビットで送られるので上位16ビットを読み捨てて(空読みして)下位16ビットを使用する形で互換を取っています。なのでホスト側では32ビットアドレスで表示されますが上位16ビットは見ないという事で:)

20251103追記:ターゲット識別情報通知の為にdbaに0xd0コマンドを追加。レスポンスは30バイト文字列固定で返す。加えて「識別」ボタンをretro μP toolに追加。

画面右上のターゲット: 〜 にターゲット情報が表示される様にしました。

dba(今回だとhc11f_v1)に0xd0コマンド処理追加↓

画面下の識別、表示、実行、書込、開始(メモリ256バイトテスト)、ロード、終了が正常に動作する事を確認致しました。m68030_v0の時と画面変わらない(あたりまえ)ので新鮮味はありませんが同じツールを8ビット/32ビットCPUで使い回せる(ホスト側のpythonコードが)のは当方にとっては有り難い話なのでこの方針で進めます。

5.まとめ

・hc11f_v1(仮称)のボードを組立、動作する様になりました(dba/retro μP toolが動く迄)。

・rlinkとターゲット(今回はhc11f_v1)を接続する為の変換基板(rlink_adp_v0)の動作も確認しました。

・今後は目標であるfuzixを導入すべく(クローンでないのでアレンジ部分で色々躓く:既にマップで苦闘中:)地道にハード/ソフトを積み上げて行きたいと考えております。

・hc11f_v1(仮称)は素材として(ベアボード10枚作ってもらったので)68hc11系のSBCとしてgccなりアセンブラで、場合によってはFLEX2の移植(SD周りが不安・・・CF対応のボードを作るかもしれない)等、使い回せたらと考えております。

6.おまけ

#最近の当方のパワーワード:80年代のarduinoを製作:)

最近YouTubeで見つけたコンテンツですが、内容は格別どうという事も無いのですが解説してる方の価値観に共感というか・・・懐かしというか・・・この方はZ80コーディング(多分アセンブラ)が夢の中で出来るそうなので(羨ましい:)当方も上記のhc11f_v1でそれにあやかれないかと・・・まあ、本人の努力次第でありますが。